## Abstraction of Cyber-Physical Interplays and Its Application to CPS Design

K. G. Shin, E. M. Atkins

University of Michigan

I. Koren, C. M. Krishna

University of Massachusetts

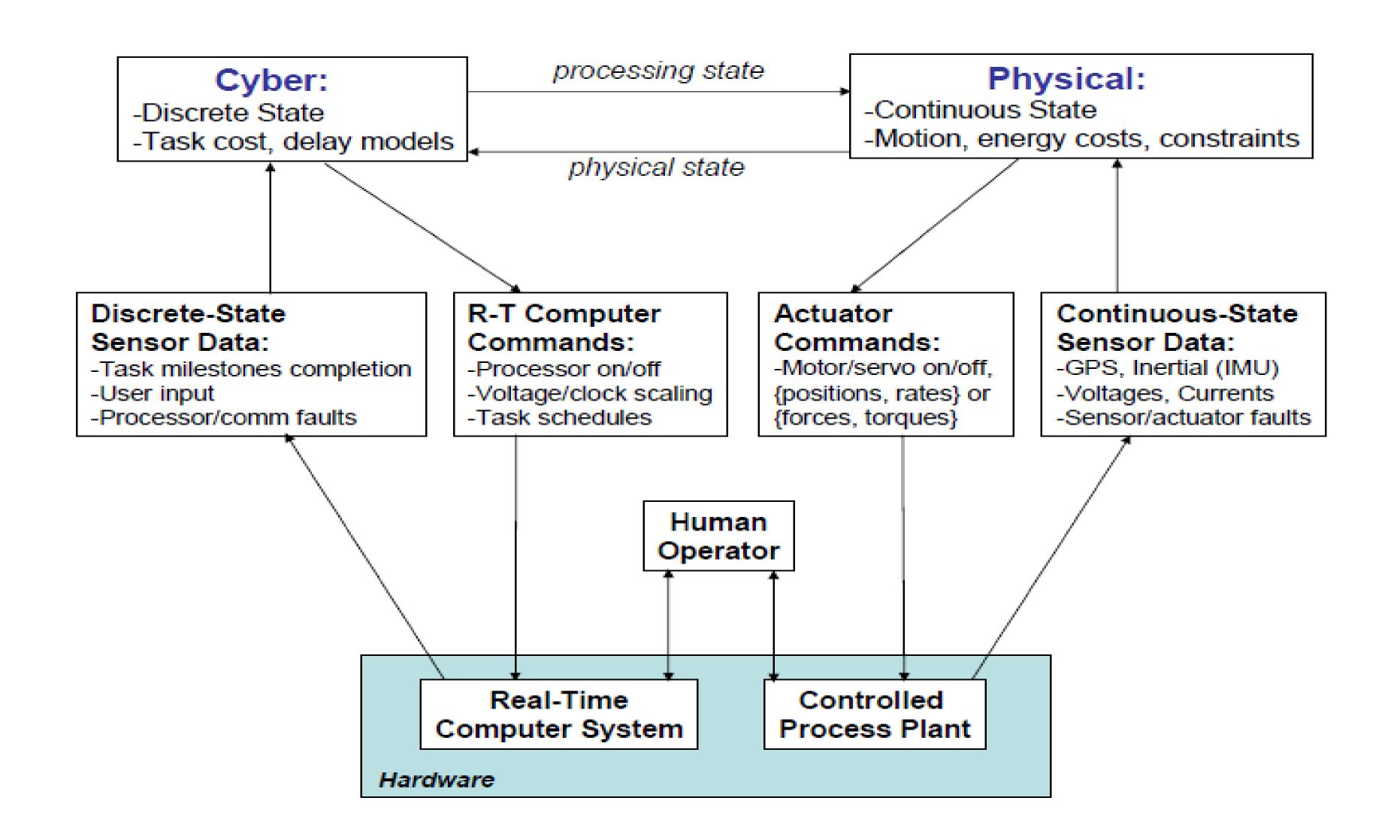

## Objective: To facilitate

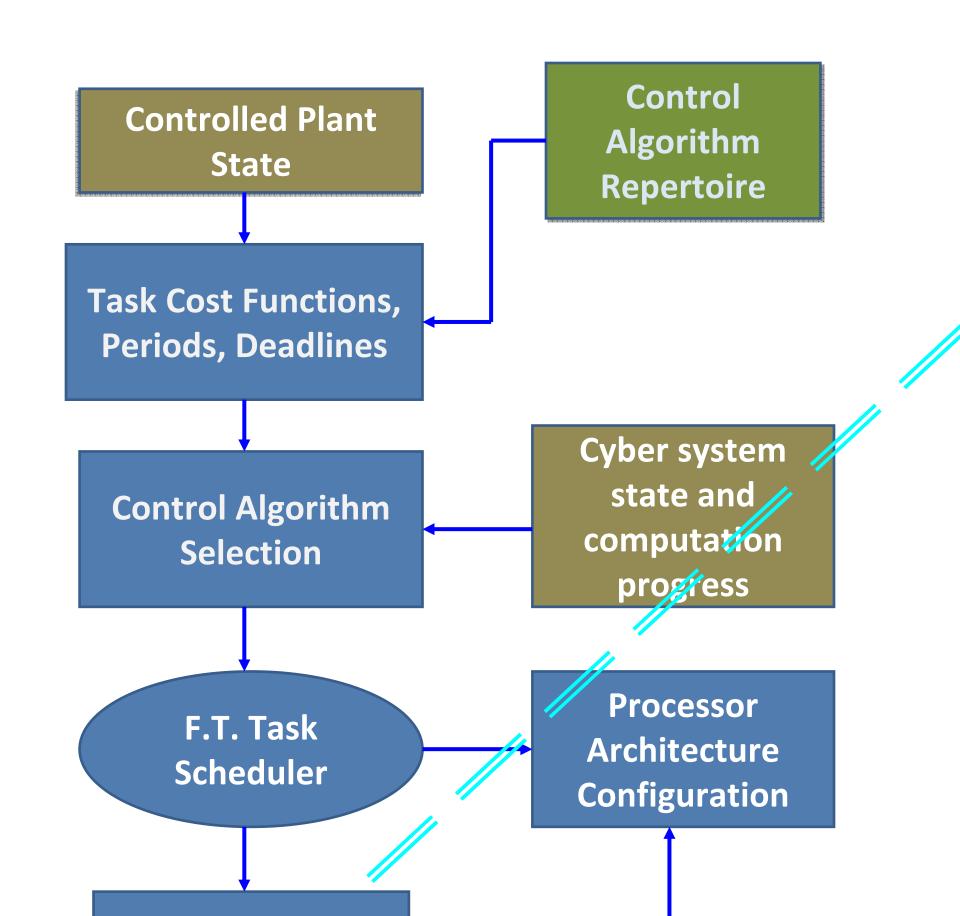

Effective codesign of real-time computer and controlled plant (offline)

Efficient online use of computational and plant resources to ensure

Fault Tolerance

Power/energy efficiency

### Superior controlled plant performance

Abstraction Duality in CPS

### Interfaces

### Application-to-Computer Interface: Specifies how the application's QoS degrades as a function of

- Current application and environmental state

- Computational delays

- Computational imprecision

- Residual mission lifetime

#### Computer-to-Application Interface: Specifies

- Task periods, precision levels, and priority rules

- Use of energy reserves

- Task milestones completion

- Computational health

## Abstraction of Cyber-Physical Interplays and Its Application to CPS Design MICHIGAN UMASS

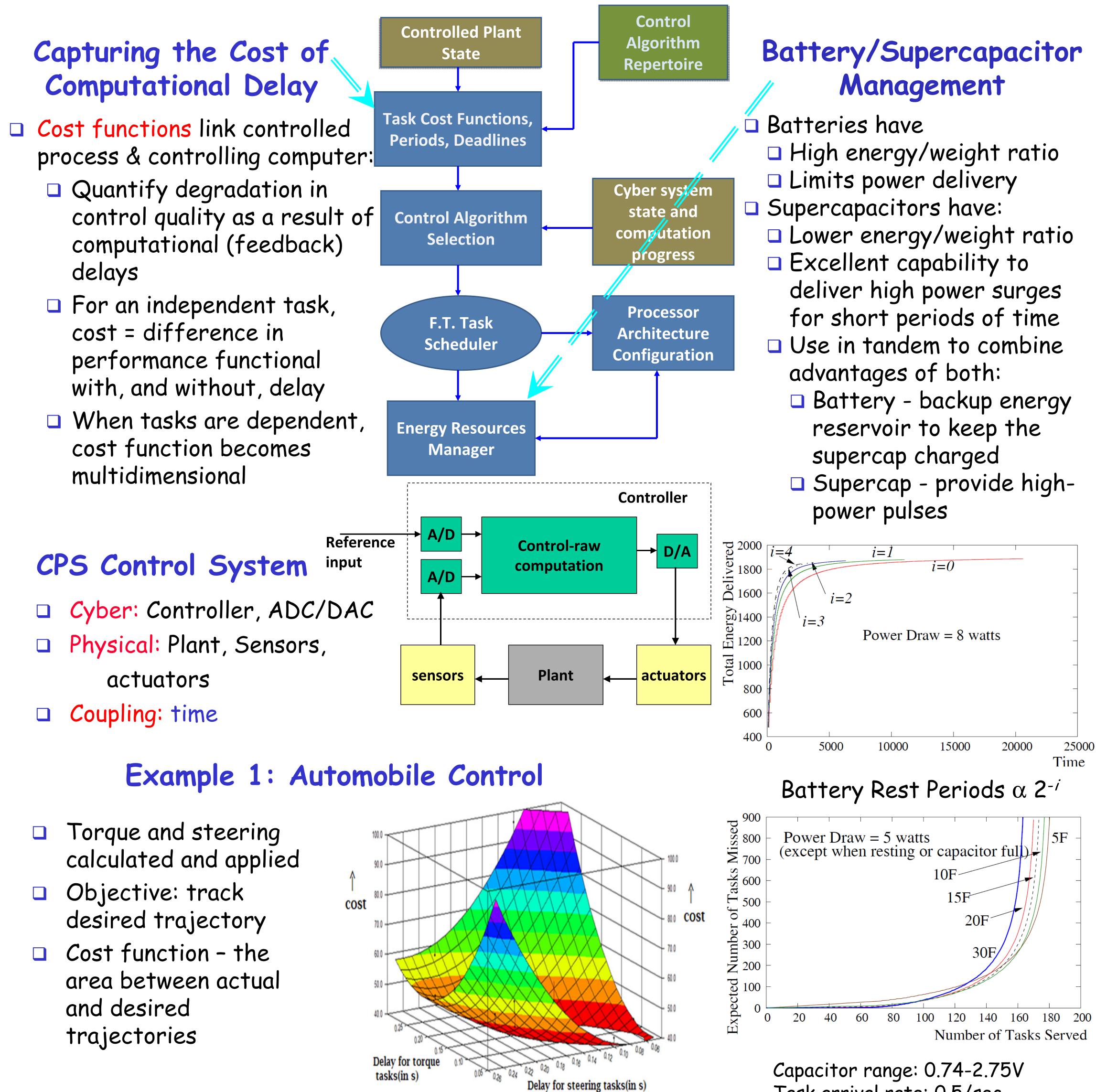

# **Computational Delay**

- Quantify degradation in computational (feedback) delays

- cost = difference in performance functional

Task arrival rate: 0.5/sec Energy per task: 10 joules

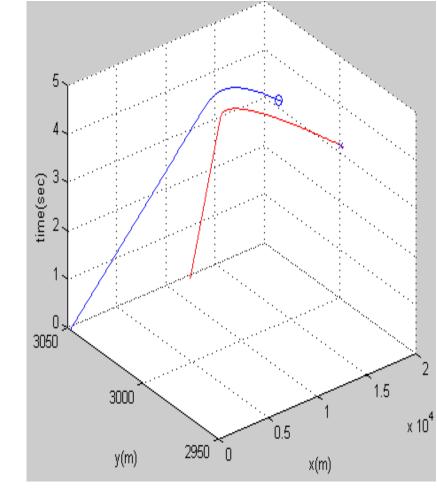

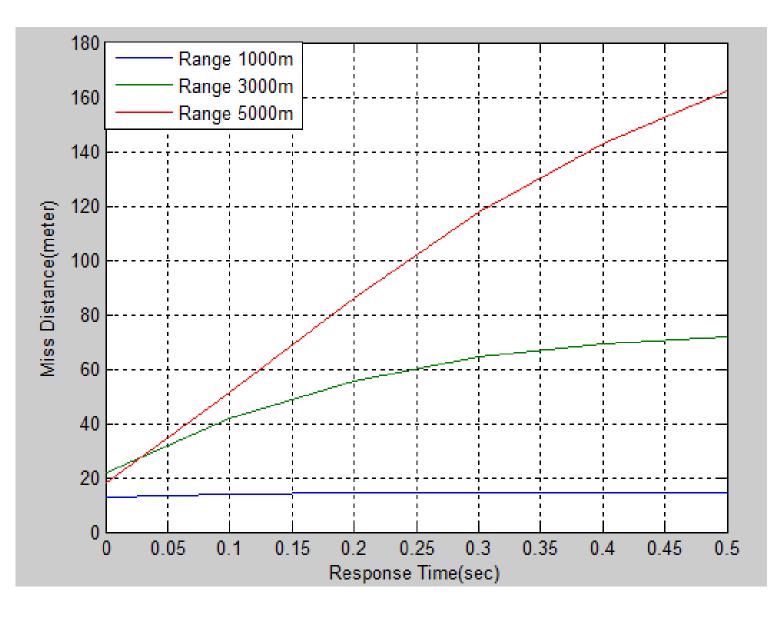

### Example 2: Chasing an evasive target

A point target maneuvering (at 10g max) when at a 3km distance from chaser

Approximated

1<sup>st</sup> order model

3050 y(m)

Computer delay 0.1s

Computer delay 0.01s

### Abstraction of Cyber-Physical Interplays and Its Application to CPS Design MICHIGAN UMASS

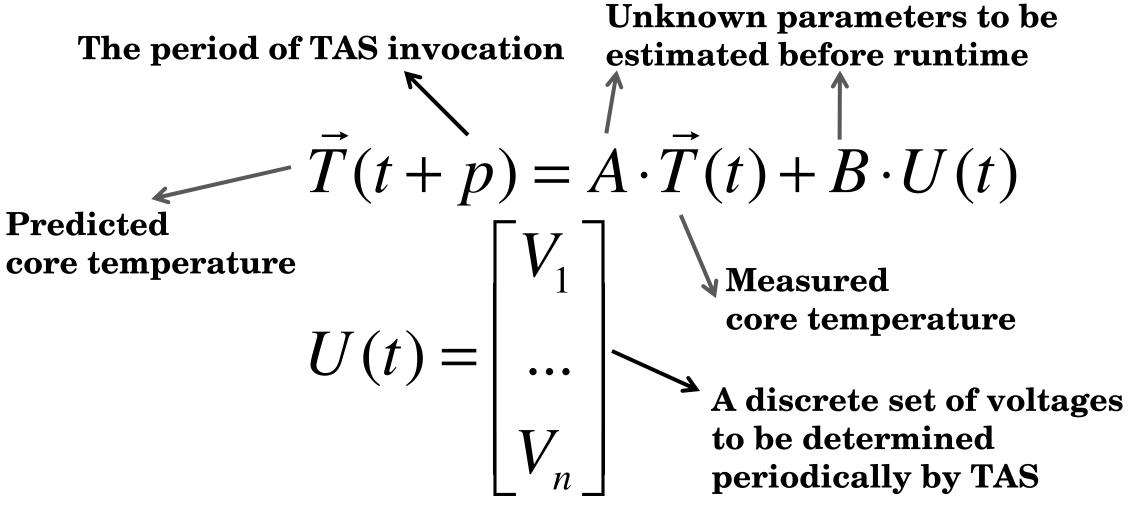

### Thermal-aware Scheduling

Thermal hazards exist in modern multi-core chips with nano-scale CMOS technolog

Large temperature variance and existence of hotspots degrade chip reliability

Approach: Minimize temperature variance on a multi-core chip while meeting the real-time application's timing constraints

**Proposed Solution**

**Energy Resources** Manager

### Results

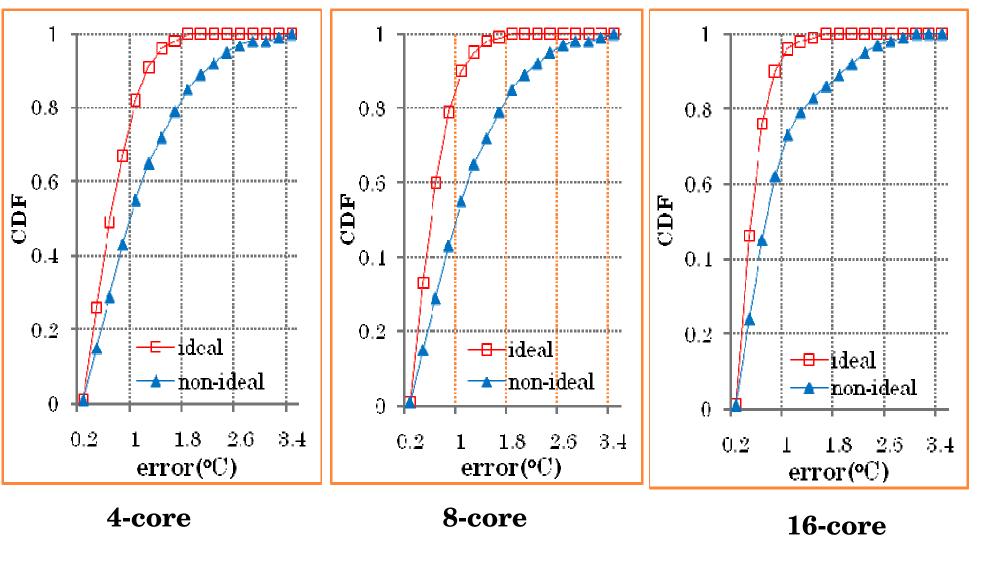

- 1. HotSpot simulator used with randomlygenerated task sets.

- 2. MCPat and Wattch power simulator used to estimate power characteristics of tasks.

- 3. Period of TAS: 40msec.

- 4. "Ideal" when all tasks have the same power dissipation.

- Assume existence of on-chip temperature sensors deployed on a multi-core chip

- Periodic measurement of core temperature

- Based on measured temperature values, a runtime Thermal-aware Scheduler (TAS) adjusts the voltage/frequency of cores periodically

- To meet the thermal constraints while guaranteeing the applications' timing constraints

- Use of per-core DVS

- On-chip regulator to guarantee the independent power/clock domain of each core

- The voltage switching overhead is tens of nano-seconds

- Use of job migration

- The speed of a hot core is reduced further by redistributing the assigned workload to other cool cores

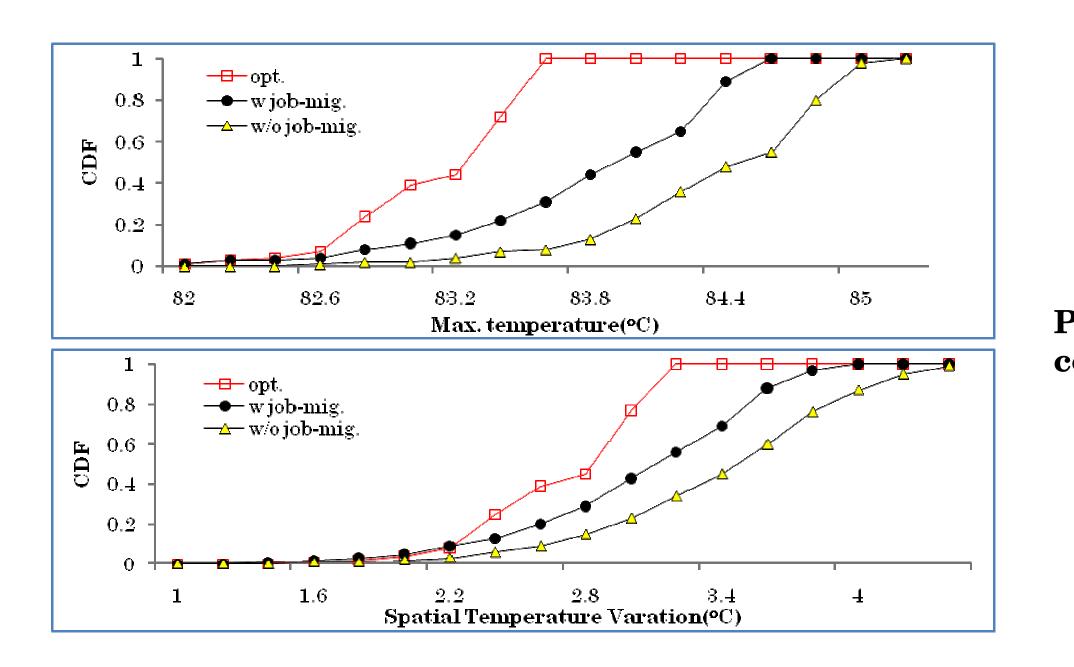

### Evaluation of the TAS

Statistics of max. core temperature and temperature variations on 16-core chip:

Obtain the thermal model of a multi-core chip

- Estimate the correlation of the voltages/frequencies of cores and their temperature behavior before runtime

- Require the warm-up period to estimate the thermal model before the system starts to operate