# Secure Split Manufacturing

JV Rajendran, UT Dallas, Email: jv.ee@utdallas.edu

Jiang Hu, Texas A&M, Email: jiang.hu@tamu.edu

### **Broader Research Goals**

- How do we protect our design from an untrusted foundries against piracy attacks?

- How can we incorporate security features into IC design tools in a low-cost fashion?

#### Objective

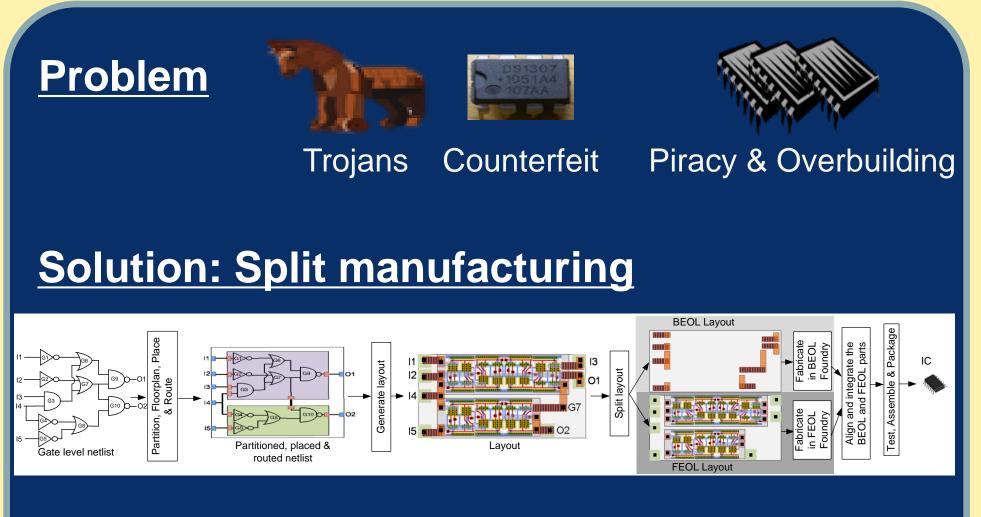

Threat Model

- Hardware is prone to supply-chain attacks

- Most attacks originate from untrusted foundry

- Avoid giving complete designs to the untrusted foundry

- Solution: Split manufacturing

- Manufacture front-end-of-line at untrusted foundry

- Manufacture back-end-of-line at trusted foundry

#### **Feasibility**

- Attacker is in the FEOL foundry; no access to BEOL

- Attacker can generate gate-level netlist from GDSII

- Resulting netlist contains gates and unknown inputoutput (IO) connections

- Attacker does not know the IO relationship of the original design

| Wire | Top metal layers<br>(BEOL) | I          | D't-L (   |

|------|----------------------------|------------|-----------|

| Via  | . J                        | Layer      | Pitch (nm |

|      | •                          | M10        | 1600      |

|      |                            | M9         | 1600      |

|      | Intermediate               | M8         | 800       |

|      | (BEOL)                     | M7         | 800       |

|      |                            | M6         | 280       |

|      | . (                        | M5         | 280       |

|      | Lower metal                | M4         | 280       |

|      | (FEOL)                     | M3         | 140       |

|      | <b>i</b>                   | M2         | 140       |

|      | Transistors<br>(FEOL)      | <b>M</b> 1 | 130       |

|      |                            | Poly       | 125       |

Different requirements in manufacturing FEOL and BEOL Leverage for security

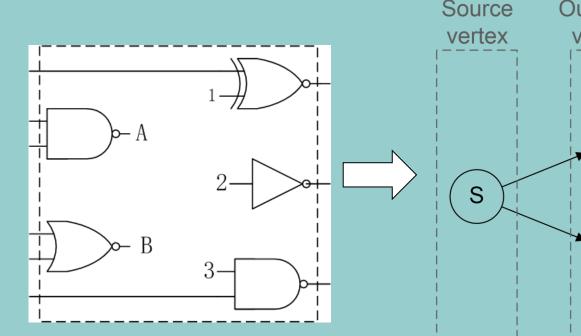

## Approach: Exploit heuristics of physical-design tools to attack

#### Hints for an attacker

- Acyclic combinational logic circuit

- Physical proximity

- Load capacitance constraint

- Timing constraint

- Directionality of dangling wires

# Output pin Input pin Target vertices vertices vertex

3

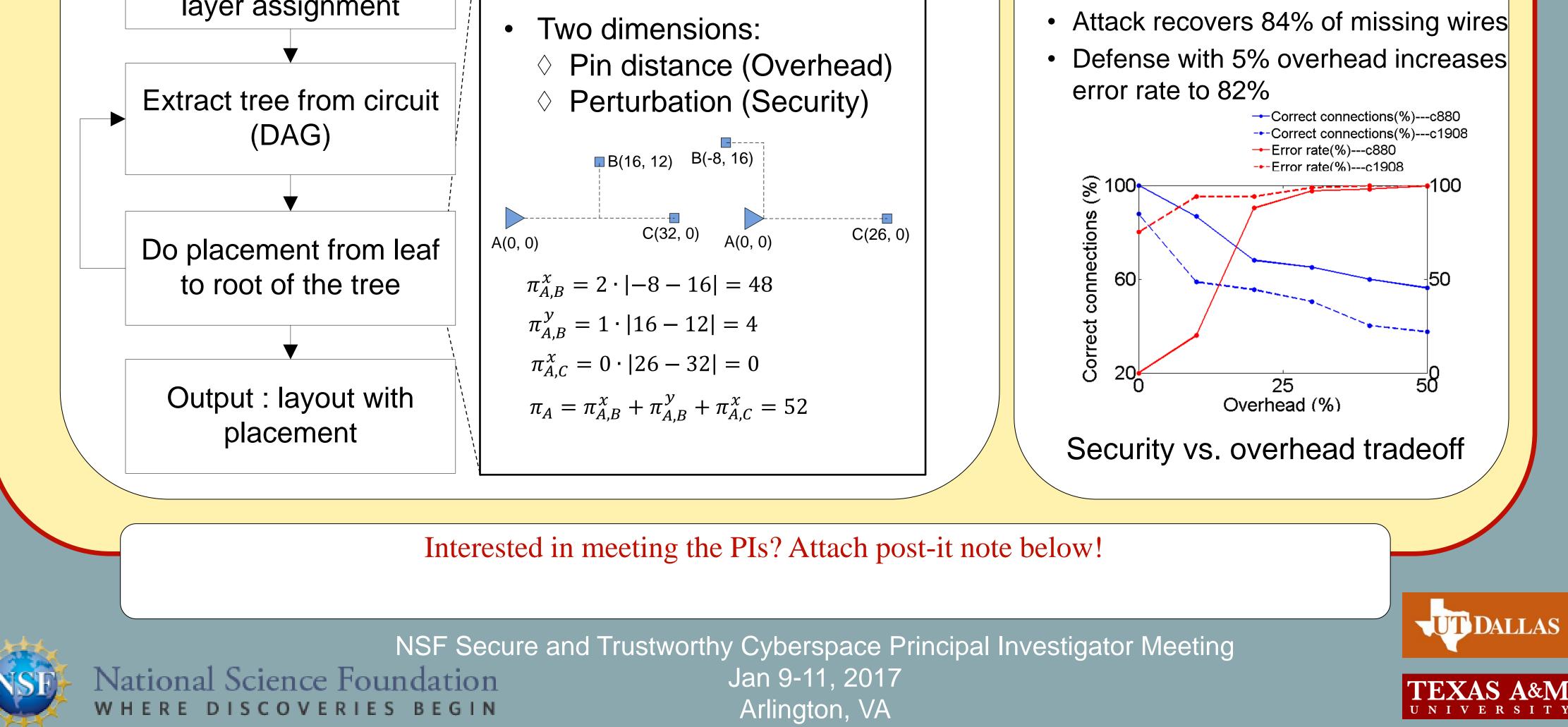

#### Defense: Placement Perturbation

Input : a design after global routing and wire layer assignment

Pareto optimization

#### Results

- Benchmark circuits: ISCAS85, ITC99

- Layout generated with Cadence tool

#### Problem formulation: Min-cost n/w flow