# Computationally Enabled, Robust, Low-Power True Random Number Generation (TRNG)

# **Key TRNG Metrics**

- Robustness (PVT/attack resistance)

- Efficiency (pJ/output-bit)

- Throughput/Bitrate (Gbps)

#### **Existing Approach: Circuit Design Driven**

- Minimize bias B=P(X=1)-0.5 (ideally 0)

- Autocorrelation ignored or an afterthought

- Fundamental limiter to Randomness

- PVT Variation induced Bias

- Finite Bandwidth, 1/f noise induced correlation between bits

## **Example: Metastability-based TRNGs** Non-white noise Correlation Offset Bias Power spectral density **Autocorrelation** R[n] Ideal (e.g. thermal) Real v

- Limit bias  $\rightarrow \mu V$  resolution offset cancellation  $\rightarrow \psi$  robustness)

- Limit Correlation  $\rightarrow$  High bandwidth circuits  $\rightarrow$   $\uparrow$  power,  $\downarrow$  bitrate)

- No clear approach to address 1/f noise

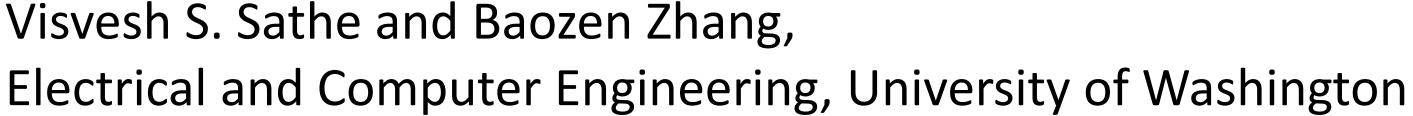

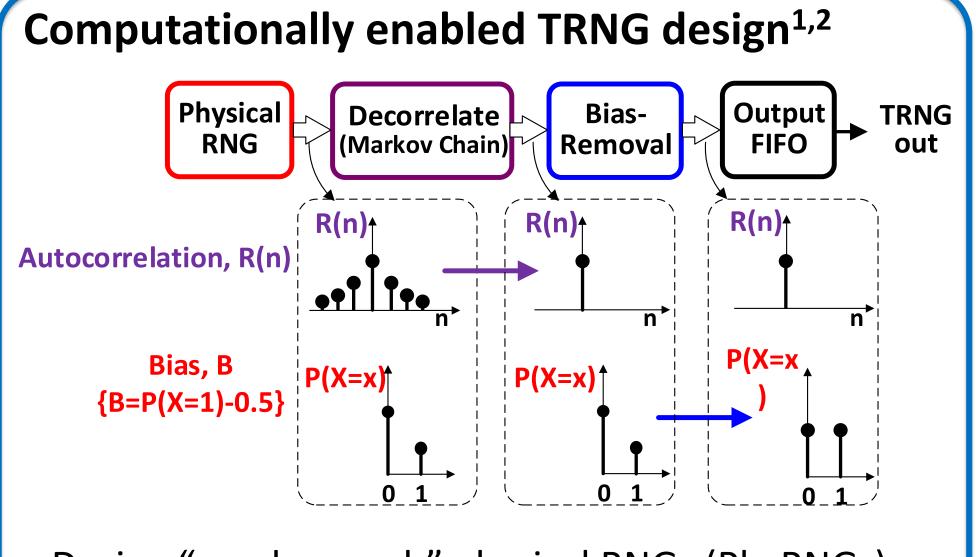

- Design "good-enough" physical RNGs (PhyRNGs)

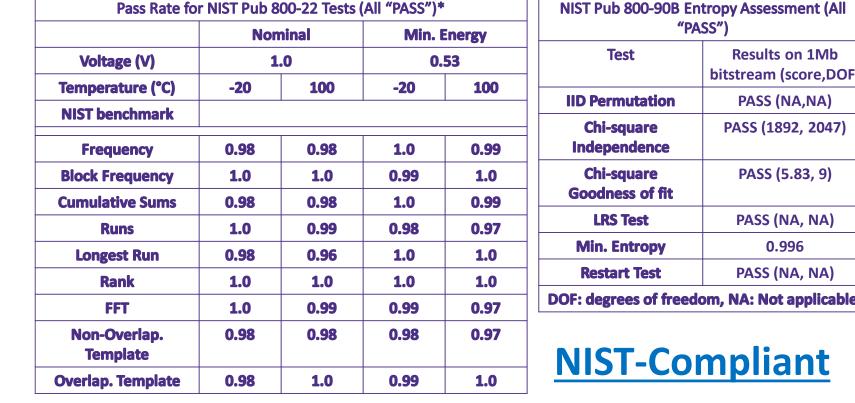

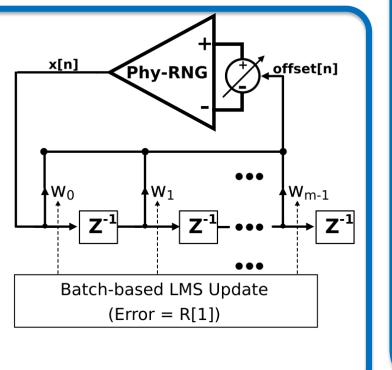

- Integrated post-processing first whitens bitstream (correlation removal), then eliminates bias

- MC whitening: Bits within channel have identical statistics

- Bias Removal using Iterative vonNeumann (IVN) correction<sup>3</sup>

- Whitening MUST precede IVN to better meet iid requirement

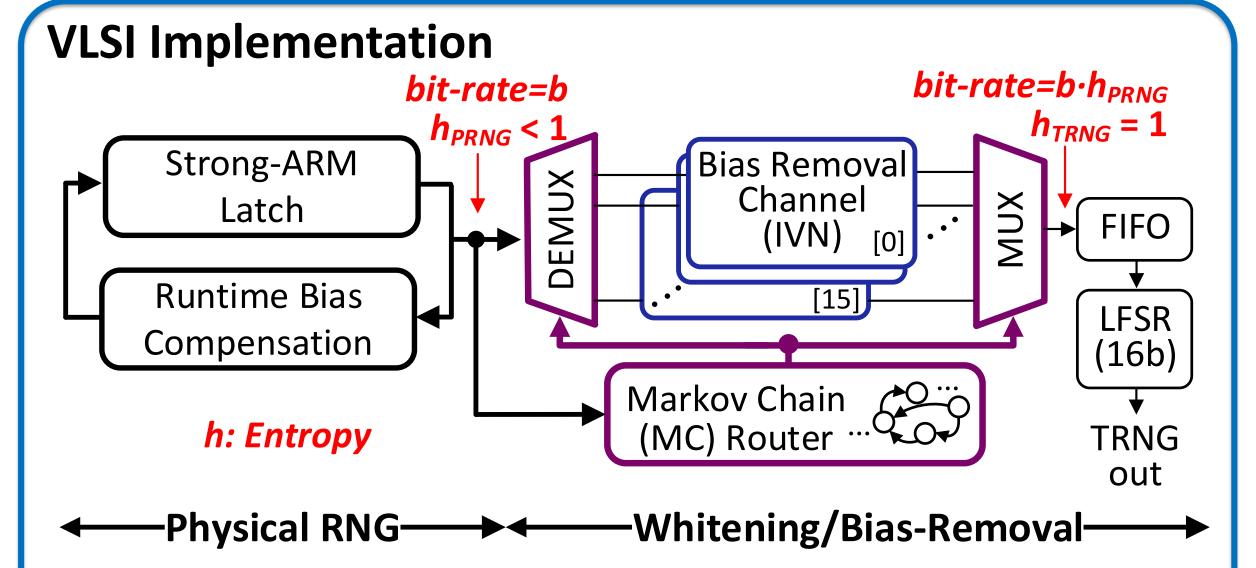

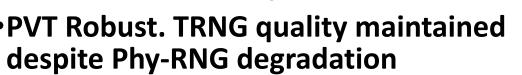

# 65nm CMOS Test-Chip Measurements

Lowest Energy/bit among NISTcompliant digital TRNGs

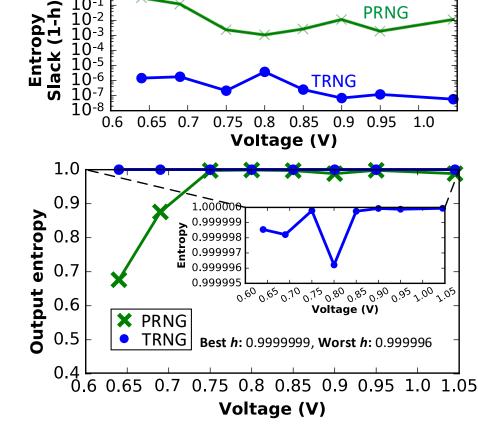

### •PVT Robust. TRNG quality maintained •Validated in the -20C-100C and 0.58V-1.0V range

#### Challenges

- Proposed TRNG architecture achieves quality, robustness, efficiency and bitrate

- Significant advance in correlation, **BUT** significant room for improvement

- MC-Router does not scale well (2<sup>n</sup> lanes required for lag-n decorrelation

- MC-based whitening addresses stationary autocorrelation sources, not non-stationary ones (e.g. 1/f noise). LFSR still required to achieve robust NIST compliance

#### **Future Work**

- **Adaptive** TRNGs

- Runtime trade-off management for optimal quality and efficiency

#### **Broader Impact**

- Aobust and balanced architecture applicable broadly applicable across TRNG implementations (FPGA/ASIC/SoCs)

- Findings covered as part of a week-long module in the Advanced VLSI design course at the University of Washington

#### References

- 1.V. Pamula et al., "An all-digital true-random-number generator with integrated de-correlation and bias correction at 3.2-to-86 Mb/s, 2.58 pJ/bit in 65-nm CMOS", In 2018 IEEE Symposium on VLSI Circuits 2018, Jun. 18

- 2. V. Pamula et al.,"A 65-nm CMOS 3.2-to-86 Mb/s 2.58 pJ/bit Highly Digital True-Random-Number Generator With Integrated De-Correlation and Bias Correction." IEEE Solid-State Circuits Letters. 2018 Dec;1(12);237-240

- 3.Y. Peres "Iterating Von Neumann's Procedure for Extracting Random Bits", The Annals of Statistics. 20. 10.1214/aos/1176348543.