# Parameter Obfuscation: A Novel Methodology for the Protection of Analog **Intellectual Property**

# Dr. Ioannis Savidis, Associate Professor, Drexel University

http://ice.ece.drexel.edu

#### **Research Interests**

Analysis, modeling, and design methodologies for high performance digital and mixed-signal integrated circuits; Emerging integrated circuit technologies; Electrical and thermal modeling and characterization, signal and power integrity, and power and clock delivery for 3-D IC technologies; On-chip power management; Low-power circuit techniques; Algorithms and methodologies for secure IC design

# LABORATORY & TEAM

### - Seven Ph.D. students

- Kyle Juretus Secure digital IC design

- Vaibhav Venugopal Rao Analog IC IP protection

- Saran Phatharodom Digital obfuscation metrics

- Zhengfeng Wu ML for analog circuit design

- Pratik Shrestha ML for digital circuit security Ziyi Chen – Analog side-channel characterization

- Shazzad Hossain Low-power sub-threshold computing

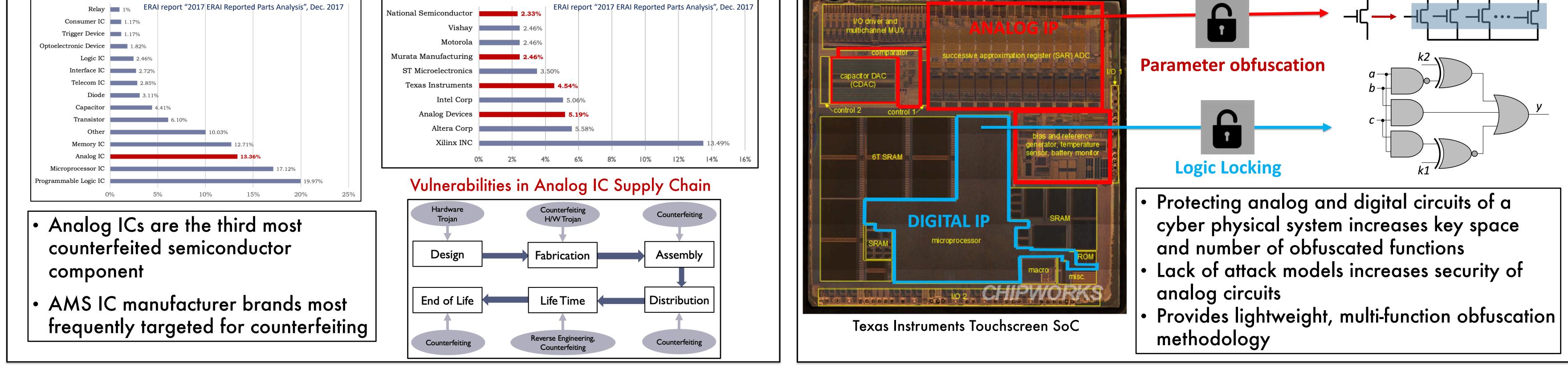

Types of Electronic Components Reported in 2017

Top 10 Manufacturer's Brands of Reported Parts in 2017

- IC overproduction

- Trojan insertion

- Counterfeiting

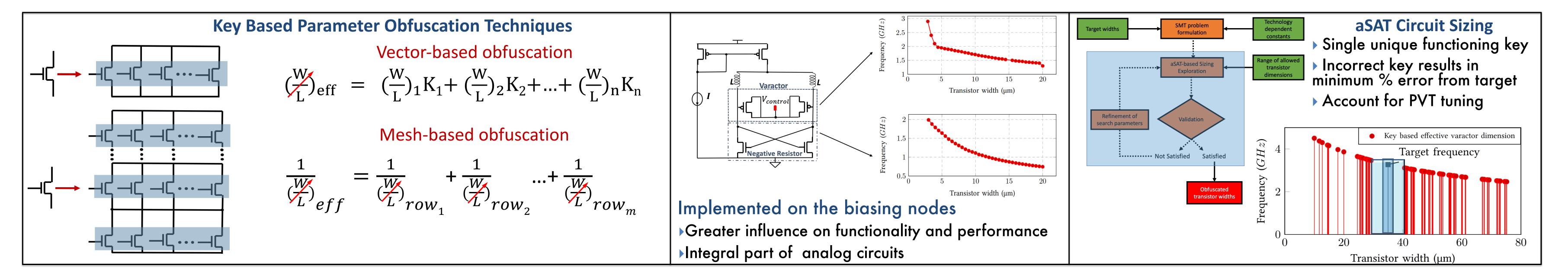

- aSAT based transistor sizing methodology reduces analog design time and complexity • Determine transistor sizes for given performance specifications • Determine obfuscation transistor sizes to produce single unique key and minimum % error for incorrect key

**SYNOPSYS**<sup>®</sup>

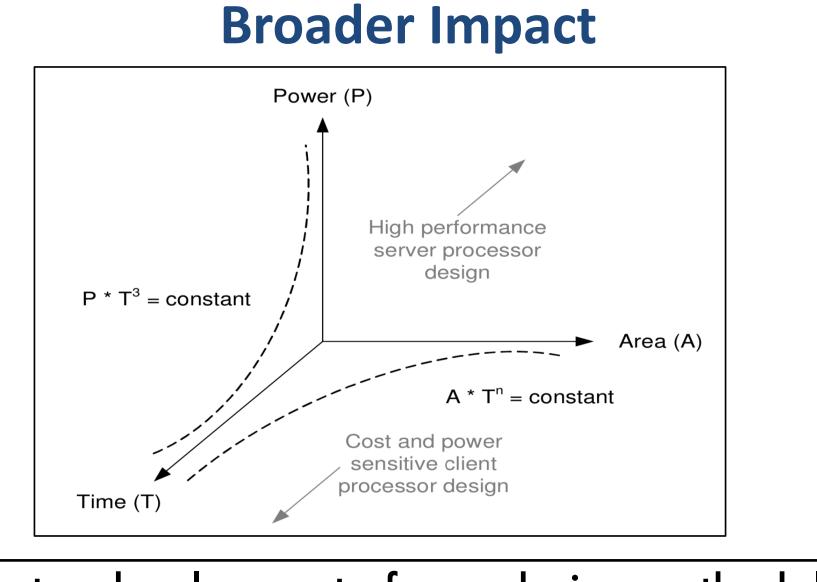

- Promotes development of new design methodologies with security as the new constraint along with power, area, and performance

- Promotes development of multi-constraint optimization algorithms

# **Potential Impact**

- Proposed technique protects against overproduction and reverse engineering from untrusted foundries

- Reduces the risk of Trojan insertions as adversary does not have complete circuit understanding

- Masks circuit functionality even for a small key size • Ideal for small IoT based circuits

- Complements logic obfuscation techniques to provide increased security of mixed-signal ICs

- Resilient against traditional SAT and side channel attacks

#### The 4<sup>th</sup> NSF Secure and Trustworthy Cyberspace Principal Investigator Meeting

October 28-29, 2019 | Alexandria, Virginia